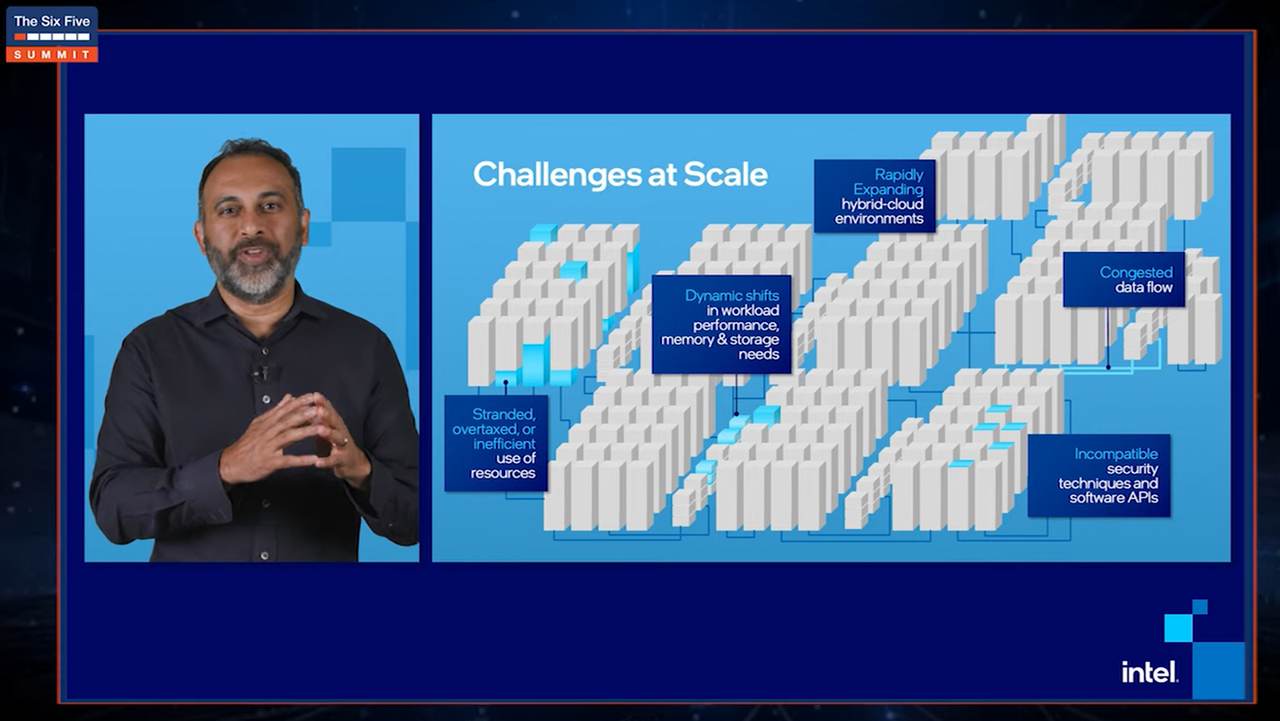

در واضح ترین تأیید تا به امروز که “C” در “CPU” ممکن است به زودی دیگر به معنای “مرکزی” نباشد ، اینتل رسماً اعلام کرد که آینده “چشم انداز” عملکردهای مدیریت سرور و شبکه در دستگاه خارج از مرکز Xeon پردازنده اینتل که این دستگاه را واحد پردازش زیرساخت (IPU) می نامد ، اکنون می گوید این م componentلفه هنوز نامی ندارد ، اپراتورهای سرویس ابری را قادر می سازد تا یک مدل مجازی سازی جدید ، انعطاف پذیرتر را اتخاذ کنند.

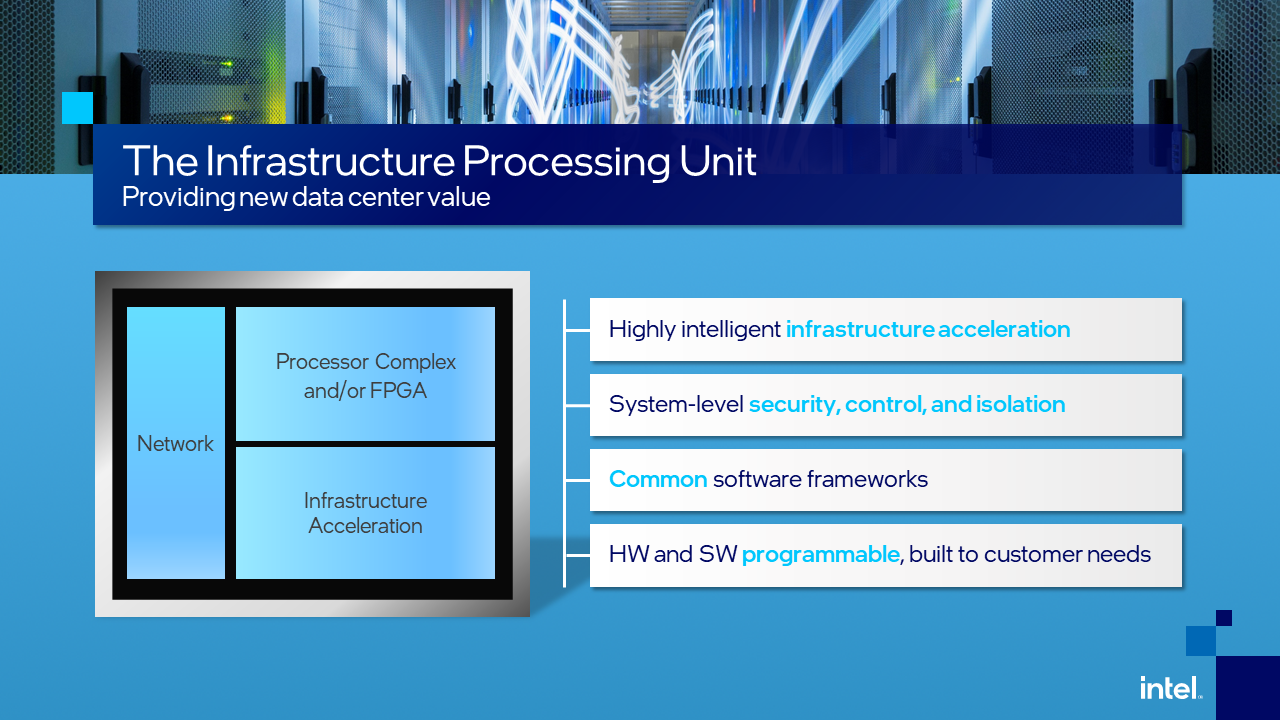

ناوین شنوی ، معاون اجرایی اینتل و مدیر کل گروه سیستم عامل داده گفت: “این یک خط تولید SmartNIC ما است.” “در صورت همراه شدن با ریزپردازنده Xeon ، شتاب زیرساخت بسیار هوشمند ارائه می شود. و این امکان را فراهم می کند که سطح جدیدی از امنیت ، کنترل ، انزوا و سیستم به شکلی قابل پیش بینی تر ارائه شود. “

حرکت امروز محور اینتل را از موقعیت 2019 خود در پردازنده های شبکه کامل می کند ، زمانی که کارت های رابط شبکه مبتنی بر FPGA (NIC) را با قابلیت برنامه ریزی متصل از طریق ASIC تولید می کند. در ماه اکتبر گذشته ، در میان تعمید دادن کارت های SmartNIC مبتنی بر Mellanox توسط Nvidia به عنوان “DPUs” و Xilinx در انتظار حرکت به سمت بالا بردن SmartNIC های خود به نقش پردازنده های مشترک (که در فوریه گذشته انجام شد) ، اینتل به طور رسمی کارت های شبکه مبتنی بر FPGA خود را لقب داد “SmartNICs” ، البته کمی دیر ، به این روند می پیوندد.

اکنون اینتل به حزب “xPU” پیوسته است که نشانگر یک تغییر بزرگ استراتژیک برای شرکت است که اکنون توسط CTO افسانه ای سابق و مدیر عامل سابق VMware ، پت گلسینگر رهبری می شود. حتی در هجوم همه گیرها ، مدیران و مدیران اینتل از CPU به عنوان اصلی ترین تامین کننده قدرت و عملکرد دفاع می کردند – در عین حال ، مسیر جدید قانون پس از مور را برای این شرکت هموار می کردند. تصدیق اینکه یک IPU می تواند بار کاری را از CPU فرض کند ، به این معنی است که اینتل دیگر از گفتن اینکه CPU می تواند با حجم کار سیستم و شبکه مدیریت شود ، بیش از حد نمی ترسد.

شنوی ادامه داد: “با مدیریت زیرساخت ها به این روش ، IPU ها می توانند دسترسی مستقیمی به حافظه و حافظه داشته باشند و محاسبات کارآمدتری ایجاد کنند ، درست است؟ Jevons Paradox اعمال می شود. “

این اشاره به مشاهداتی است که توسط اقتصاددان انگلیسی قرن نوزدهم ویلیام جوونز انجام شده است – یعنی اینکه افزایش کارایی یک منبع انرژی باعث افزایش مصرف خود می شود. این کمی از قانون مور قدیمی تر و خسته کننده تر است ، اما ممکن است مجبور به انجام وظیفه کامل باشد تا زمانی که کسی نظریه مدرن تری را برای اقتصاد مقیاس اینتل تولید کند.

لیزا اسپلمن ، نایب رئیس و مدیر کل محصولات Xeon اینتل ، در مصاحبه اخیر خود با Data Center Knowledge اظهار داشت: “این نمونه کارها مبتنی بر درک محدودیت هایی است که افزایش تقاضا ایجاد می کند و سپس پرداختن به آنها و از بین بردن آنها.”

اسپلمن ادامه داد: “SmartNIC های ما به شما كمك می كنند تا با مدیریت زیرساخت ها كنار بروید ، در داخل گره یا دندانه دار باشید. و سپس برخی از کارهایی که ما با CPU و XPU انجام می دهیم منجر به گزینه شتاب تفکیک شده می شود: چندین گره که به عنوان یک سیستم کنار هم کار می کنند. “

به طور وسوسه انگیزی که در اطلاعیه رسمی اینتل در روز دوشنبه حذف شده است ، استفاده از کلمه “سرور” در خارج از یک زمینه تاریخی است. این درها را کاملاً برای اینتل باز می گذارد تا نه تنها در تولید اجزای تفکیک شده ، بلکه در همکاری با آنها همکاری کند. همانطور که اسپلمن آنها را توصیف کرد ، اینها مجموعه های مستقلی از منابع جمع شده خواهند بود که احتمالاً برای معماری در مقیاس رک طراحی شده اند.

“قبلاً همه محاسبات روی پردازنده ها انجام می شد. این به وضوح در حال تغییر است ، “اظهار داشت Guido Appenzeller ، اینتل که اخیراً CTO را برای گروه سیستم عامل داده خود منصوب کرده است ، در مصاحبه با Data Center Knowledge. “ما در حال ظهور GPU ها ، شتاب دهنده های هوش مصنوعی ، IPU هستیم. ما شاهد تنوع بیشتر ، ناهمگنی بیشتر هستیم. این قطعاً یک روند است و ما آن را پذیرفته ایم.

![مرکز داده_نمایش آینده [1200 px].jpg](https://www.datacenterknowledge.com/sites/datacenterknowledge.com/files/DataCenter_of_theFuture_slide%201200%20px.jpg)

Appenzeller ادامه داد: “اگر به مرکز داده آینده نگاه می کنید ،” مدل کلاسیک سرور … بسیار سخت است. این ایده که یک پردازنده مرکزی باید بین هر شتاب دهنده ای قرار بگیرد – این که یک شتاب دهنده باید از طریق CPU به شبکه متصل شود ، سپس کارت شبکه ، سپس پارچه ایجاد شود – فکر می کنم دیگر این کار ادامه ندارد. در آینده ، این بسیار پیچیده تر خواهد شد. ما شاهد چند طعم از آن هستیم. ما یک واحد پردازش زیرساخت را می بینیم که در مقابل این شتاب دهنده های ذخیره سازی قرار دارد. و در فضای هوش مصنوعی ، ما شاهد پارچه های خصوصی هستیم ، جایی که شما دو کارت شتاب دهنده دارید که پارچه های خاص خود را دارند ، زیرا آنها نیاز به انتقال چنین مقدار زیادی حافظه در تأخیرهای بسیار کم دارند. “

با انتقال سرورهای hyperscale به سیستم عامل هایی که از مراکز ارتباطی پشتیبانی می کنند ، تأخیرها هم قابل اندازه گیری و هم برجسته تر می شوند. میزان اطمینان CPU برای تأمین بارهای کلاس سازمانی ممکن است گهگاه در چند ثانیه اندازه گیری شود ، اما هنگامی که ابزارهای مورد استفاده در میلی ثانیه شروع به اندازه گیری می کنند ، می دانید که با محدودیت های شبکه ارتباطی روبرو هستید.

و این محدودیت ها ممکن است از قبل برای طراحی پردازنده ای بسیار سخت و طاقت فرسا شده باشند که به هر حال ، فقط یک قدم نسبت به گذرگاه ISA ایجاد شده برای رایانه شخصی IBM فاصله دارد. رویای بسیاری از سازندگان سرور ، که برخی تمایل دارند با صدای بلند بگویند ، این است که حافظه با استفاده از یک شبکه سریع که بتواند جایگزین گذرگاه سیستم شود ، قابل آدرس دهی شود.

منطقی نیست که پردازنده مرکزی – امروزه داور سیستم گذرگاه سیستم – مسئولیتهای مدیریت خود را به ساختار شبکه منتقل کند. پذیرفتن نقش یک پردازنده زیرساختی ، خواه از نامه اینتل برای آن استفاده کنید یا از انویدیا ، ممکن است بزرگترین گام در جهت شبکه سازی DRAM در جعبه های مقیاس رک باشد. این می تواند بازار سرورهای فوق مقیاس را به طور گسترده باز کند – آنقدر گسترده است که سرورهای جداگانه دیگر عامل شکل دهنده نیستند.

ناوین شنوی در اطلاعیه روز دوشنبه اظهار داشت: “ما قبلاً IPU ها را با استفاده از FPGA مستقر کرده ایم ،” با حجم بسیار بالا در Microsoft Azure. و ما اخیراً همکاری با Baidu ، JD Cloud و VMware را نیز اعلام کردیم. “

شنوی اعلامیه خود را به عنوان بخشی از نشست شش اجلاس سران با عنوان “چرا شما به اشتباه درباره آینده مرکز داده فکر کرده اید” ارائه داد. “شما” ، در این زمینه ، احتمالاً خود شما هستید ، که به دلیل درک سرورها فقط به عنوان جعبه هایی با اتوبوس های سرویس و رابط های شبکه در تمام این سال ها سرزنش می شوید. (شرم آور ، شرمنده شما ، که اجازه داده اید خود را گمراه کنید … خوب ، توسط اینتل.)

متن اعلامیه رسمی اینتل ، IPU ها را به عنوان شتاب دهنده های زیرساخت در کنار XPU ها (بزرگ “X”) طبقه بندی می کند ، که آنها را به عنوان “برای شتاب مخصوص برنامه یا کار خاص” طبقه بندی می کند. اینتل سازنده شتاب دهنده FPGA Altera را در سال 2015 خریداری کرد و در جریان عرضه نسل سوم Xeon در آوریل گذشته ، FPGA خود را در ردیف جلو قرار داد.

اینتل همچنین در مورد ارتقاable احتمالی نقش واحدهای حافظه حالت جامد Optane خود اشاره کرده است. این شرکت که با CPU ، XPU و اکنون IPU همراه است ، به وضوح به نظر می رسد که یک “پلت فرم Xeon” را مونتاژ می کند ، احتمالاً با برنامه آرم خود. می توان سرورهای متداول و همچنین لوازم سرویس مبتنی بر Xeon را در مقیاس rack به عنوان یک آرم صدور گواهینامه Intel ارتقا داد ، شاید با شعاری مانند “Xeon-based”.

چنین برنامه بازاریابی می تواند اینتل را در برابر رقابت سریع سازندگان پردازنده Arm مانند Ampere در یک به یک قرار دهد و به مشتریان با حجم بالا مانند Microsoft Azure واضح تر ، آشنا تر و شاید کمتر اضطراب آور باشد. انتخاب ها امیدوارم تا آن زمان ، آن دسته از مشتریان به فکر آینده مرکز داده نباشند.

روز دوشنبه ، اینتل بلافاصله مارک خط تولید SmartNIC موجود خود و همچنین SmartNIC های شریک ساخته شده با پردازنده های Intel Stratix FPGA را با نام “واحدهای پردازش زیرساخت از اینتل” آغاز کرد. به عنوان مثال ، آداپتور شبکه چهار پورت 100 گیگابایتی Silicom N5010 موجود در حال حاضر در وب سایت اینتل ظاهر می شود که به عنوان “آداپتور IPU” ذکر شده است.